Access:8

FPGA/HDL/論理回路

論理変換から信号処理,Linux SoC,PythonやCを利用した高位合成まで,高速処理に欠かせないプログラマブル・ディジタル・ハードウェアの教材や解説です.

ZEPマガジン

|

HDL500行!ミニRISC-Vマイコンの実力 HDL500行で構築した自作RISCマイコンを処理速度をDhrystoneベンチマークで評価.対象はRV32Iアーキテクチャで,命令数は非常に限定され,整数演算だけを実装 |

|

CPU/RAMからROM/I/Oまで!ミニRISC-Vマイコンの構成 FPGAキットDE10上に構築した自作のミニRISC-Vマイコンは,CPU,ROM,RAM,SDRAMといった基本的なメモリ構成をもつ |

|

命令デコーダの役割と動き:実行回路用の制御信号作り 命令デコーダはCPU内部で各命令を解析し,実行回路に必要な制御信号を生成する重要なブロック |

|

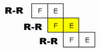

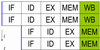

RISC-V 自作ミニCPUの3段パイプライン命令処理 自作したCPUはRV32I命令セットをベースにした超ミニRISC-Vで,3段のパイプラインを採用している |

|

CPUの基本:命令は3ステップ処理 CPUが命令を処理する最初のステップは命令フェッチ,次が命令デコード,最後が命令実行 |

|

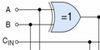

初めてのHDL記述「組み合わせ回路」 HDLでの組み合わせ回路の記述は,System VerilogやVerilog 1995/2001において2つの方法がある |

|

コンピュータのメカニズム CPUは計算や制御の中心であり、各種記憶素子や周辺機能とデータをやり取りする役割を担う |

|

HDLソース 500行のミニCPUを一緒に作る C言語でソフトウェア開発が行える環境を整備した HDLコード約500行のRISC-V ミニCPUを開発.シンプルながらパイプライン構造を備える |

|

Xyloniボード上の全リソースを活用するプログラム Xyloniボードに搭載されたプッシュ・ボタン,LED,SDカード・スロットの全機能を利用するプログラムXyloni_BoardTestを制作 |

|

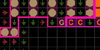

コンピュータ対戦型Tic-Tac-Toeゲームの作成 Tic-Tac-Toeゲームは3×3のマスで行う二人零和有限確定完全情報ゲーム.すべての手がオープンに共有される構造で,アルゴリズムの実装と検証に非常に適する |

|

超小型XyloniボードにRISC-V Sapphire SoCを実装する Interface Designerは,FPGA内の周辺機能と物理端子との橋渡しを行うツール.Efinityにおいて,論理設計と物理設計を明確に分離するという設計思想を反映している |

|

超小型Xyloniボードで動かすRISC-V Sapphire SoC Xyloniは,USBコネクタ,ユーザ用ボタン,LED,SDカード・スロットといった実用的なI/Oを搭載.制御信号はTrion T8 FPGAに直結しており,ユーザ・ロジックから自由に制御できる |

|

Efinix社のRISC-V IPコア Sapphire SoC Sapphire SoCは,RISC-Vアーキテクチャをベースとした32ビットCPUコアと多様な周辺機能を組み合わせたIPコア.VexRiscvをコアに据え,パイプライン処理や割込み対応,例外処理などを網羅 |

|

オープンソースな命令セットRISC-V RISC-Vは自由に扱えるISA.FPGAとの組み合わせにより,アーキテクチャを自分で設計し,学ぶことができる |

|

Efinix社のFPGA Efinix社のTrion FPGAは,安価ながらも高い柔軟性をもち,RISC-Vプロセッサの実装も可能.40nmプロセスのTrionシリーズは,I$^$2CやSPIに加えて,DDRやLVDSにも対応する |

|

自作CPU入門8:プログラミングしやすい回路作り CPUを自作するならプログラムを効率的に動かすために,割り込み処理やパイプライン,スタックなどを導入したい |

|

自作CPU入門7:CPU内部の回路 CPU内部のレジスタは,フリップフロップという回路素子で作る.レジスタの間の通信経路はセレクタという回路素子を組み合わせて作る.計算回路は加算回路を組み合わて作る |

|

自作CPU入門6:CPU内部の動き プログラム・カウンタとバス制御信号の適切な実装がCPUの安定動作の鍵.各命令の実行ステップを定義し,クロック信号に同期した状態遷移を設計する |

|

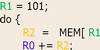

自作CPU入門5:ミニマムCPUの命令セット CPUの命令セットを設計するときは,データの入出力,ジャンプ,レジスタの活用を考慮し,回路をシンプルに,そしてプログラムを記述しやすくする必要がある |

|

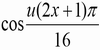

自作CPU入門4:CPUが演算を処理するメカニズム CPUは複雑な三角関数の計算やデータ処理を,加算や論理回路といった単純な動作に分解して実現する |

|

自作CPU入門3:メモリマップとアドレス CPUは,メモリマップを利用して,メモリやI/Oの位置をアドレスで指定し,正しくデータ送受信を実現する |

|

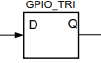

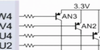

Cortex-A9内蔵FPGA“Zynq”入門 GPIO回路の設置とARM CPUとの接続 AXI4-Liteバスを使用することで,PS側のソフトウェアからレジスタ制御を行い,GPIOの状態を変更できる |

|

Cortex-A9内蔵FPGA“Zynq”入門 AXIバス経由でLチカ AXI GPIOのレジスタを操作してLEDの点灯制御を行ってみた.VivadoとVitisを組み合わせることで,ハードウェアからソフトウェアまで一貫した設計が可能 |

|

Cortex-A9内蔵FPGA“Zynq”入門 割り込み処理の実現 Zynqの割り込みシステムでは,PL側で発生したイベントをIRQ_F2P(Interrupt Request from FPGA to Processor)ポートを介してPSに通知 |

|

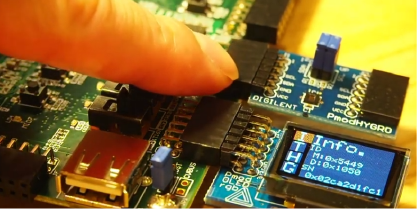

Cortex-A9内蔵FPGA Zynq 入門 アプリ層とBSP層の接続 BSP APIを利用してI$^2$Cインターフェースの温湿度センサHDC1080を制御するハードウェアとソフトウェアをZynq-7000に実装 |

|

Cortex-A9内蔵FPGA Zynq 入門 FreeRTOSのススメ Zynqでは,FreeRTOSを活用して,リアルタイム性を確保したシンプルなコーディングを実践したい |

|

自作CPU入門2:部品どうしをつなぐ「バス」 コンピュータを構成するCPU,メモリ,I/Oは,相互にデータをやり取りするために同じ通信路を共有し,同時に1つの通信しか発生しないようにルールを決めて利用する |

|

回路の動作を決めるHDLソース(.v),物理的な接続の定義ファイル(.xdc) FPGAの設計にはHDLソースと制約ファイルが不可欠.HDLは回路の動作を記述し,制約ファイルはFPGAと外部デバイスの接続を定義するもの |

|

ターゲットFPGAボード Basys 3に回路を実装 FPGAのバイナリ・データはSRAMにロードされるため,電源OFFとともに消失する.解決法は,外部フラッシュ・メモリにバイナリを保存し,電源投入時に自動的にロード |

|

初めてのHDL記述 ロジック回路設計の初めの一歩も「Lチカ」.Velilog HDLで回路を記述して,Xilinx製FPGAスタータキット BASYS 3に実装 |

|

FPGA入門 演算回路の動作テスト 平方根計算を始めとする演算回路では,MSBから1ビットずつ計算を行うアルゴリズムが用いられ,検証には総当たり,コーナ・ケース,ランダム・テストなどが有効 |

|

自作CPU入門1:コンピュータの頭脳を理解する CPUを自作することは,コンピュータの本質を理解するための実践的なアプローチだ.CPU,メモリ,I/Oの連携を学ぶことで,コンピュータの動作原理が明確になる |

|

Xilinx FPGA入門 回路バイナリの合成 Xilinx製FPGAの統合開発環境“Vivado”では,プロジェクト作成からバイナリ生成までの全工程をGUIで操作できる.合成後には,LUTやFFの使用量,消費電力の見積もり情報も得られる |

|

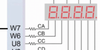

FPGA×HDL超入門 4桁の7segLED制御 Verilog HDLでは,`reg`で宣言されるレジスタは,次のクロック立ち上がり時に値を保持する重要な役割を果たす.4桁7セグメントLEDの制御回路の正しい記述は? |

|

FPGA×HDL入門 レジスタの同期運転 レジスタの同期運転は,信頼性の高い回路を構築するための基本だ.同一クロック源を用い,レジスタの値を同期的に更新することを徹底することで,設計が簡単になりエラーの発生率も低下する |

|

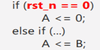

FPGA×HDL超入門 2種類のリセット回路 FPGAやLSIの電源投入後は,レジスタやフリップフロップの初期値が不定だ.意図した初期状態の保証に欠かせまいリセット処理にはクロック非同期型と同期型を使い分けたい |

|

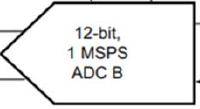

Artix-7 FPGA入門 A-D変換回路の実験 Artix-7 FPGAはアナログ電圧をディジタル値に変換する12ビット分解能のADCモジュールを搭載している.2チャネルの入力信号を扱い,154k~1000kサンプル/秒に設定できる |

|

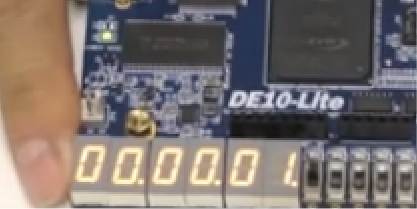

FPGAキット DE10入門 正しく動かない乗算器 正しく動かない演算回路が生成される問題を回避するためには,ビット幅を明示的に指定し,意図しない切り捨てや拡張を避けるverilogを記述することが重要 |

|

ARM/RISC-VからMicroBlazeまで Zynq-7000 SoCやZynq UltraScale+ MPSoCは,ARM Cortex-A9やCortex-A53を,Arria 10やCyclone Vは,ARM Cortex-A9を,AgilexやStratix 10は,ARM Cortex-A53やA72を搭載する |

|

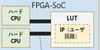

別チップ派?ハードCPU派?ソフトCPU派? Zynq FPGAは,Xilinx社が提供するFPGAとCPUを統合したSoC(System on Chip).CPUとロジックIPの構成方法において3つの選択肢が存在する |

|

自作のIPコアとメモリ/CPUをオンチップ・バス“AXI”で接続 Zynqでは,自作のIPコアとXilinx標準のIPコアを使える.IPコアは,ARM社のデータ通信用オンチップ・バス“AXI”を使ってメモリやCPUとつなぐ |

|

一時データ保存回路 レジスタの活用 ZynqはCPUと自作回路の通信バスを備える.CPUのアドレス空間上に自作回路を制御するレジスタを配置し,このアドレスを利用するメモリ・マップトI/O方式で自作回路を制御する |

|

ソフトCPU MicroBlazeとARMでLチカ MicroBlazeはProgrammable Logic部に実装するソフトCPU.Processing System部にはARMプロセッサが実装されている.Zynqでは両者を連携させたシステムを構築可能 |

|

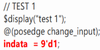

FPGAキット DE10入門 論理合成前の動作確認 FPGA設計に早く確実に成功するためには,シミュレーションによる事前確認が欠かせない.ModelSimを用いたシミュレーションの実践がかぎを握る |

|

FPGAキット DE10入門 PWM信号生成回路IP FPGAの標準インターフェースAvalonバスを利用すれば,独自IPを作りシステム統合できる.Avalonバスを介してレジスタを操作し,外部端子からPWM信号を出力するHDLソースを示す |

|

ラズパイで入門!自作RISC-VのC/C++開発環境 ラズベリー・パイやUbuntuの利用を前提に,無料の命令セット・アーキテクチャ“RISC-V”のプログラミング開発環境のセットアップ方法を解説します |

|

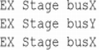

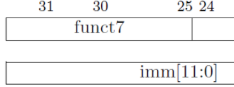

自作RISC-V パイプラインCPUの設計 RISC-Vプロセッサの重要な機能の1つが,効率的なメモリ・アクセス制御です.特に,ロード命令の処理には複数のステージが関わり,これにより命令のパイプラインが適切に動作します |

|

超入門!スイッチ読み取り回路とLED駆動回路のHDLソースコード 高速処理に欠かせないFPGA開発の第1歩は,動作確認済みのHDLソースコードをスタータキットに書き込んで,スイッチONでLEDが点くシンプルな回路を動かしてみることだ |

|

自作時代到来!オープンソースCPU“RISC-V”誕生 RISC-Vは,ISAだけが定義された自作CPU.IDE,デバッガ,RTOS,BSP,ミドルウェアなど開発にツールやリソースが豊富に揃っている |

|

正しく回路が生成されないHDL記述 論理回路設計に不可欠なハードウェア記述言語 HDLの記述が文法的に正しくシミュレーションできたとしても回路に変換できるとは限らない.動画では失敗事例を3つ紹介 |

|

米国 Efinix 社製 FPGA スタータキット“ Xyloni ”入門 米国FPGAメーカ Efinix社のモバイル/IoT向け小規模 FPGA“Trion”を搭載したスタータキット Xyloniの開発環境のインストール方法とLED点灯回路の論理回路設計を解説する |

VOD教材[視聴無制限]

|

[VOD/KIT/data]新人技術者のためのRISC-V CPU設計 初めの一歩 C言語完全対応!HDLソース 500行のミニCPUを一緒に作る |

|

[VOD/KIT]Tiny FPGA実習!高校生から始めるHDLプログラミング FPGA&Linux搭載Zynqの環境構築や使い方の基本を学ぶ |

|

[VOD/KIT]Zynqで初めてのFPGA×Linux I/O搭載カスタムSoC製作 開発環境の設定からプロセッサと自作IPの統合,高位合成,Linux上のCPUアプリ開発まで |

|

[VOD/KIT]Xilinx製FPGAで始めるHDL回路設計入門 入手性の良いスタータキットで世界の定番 Xilinx社製FPGAの使い方をマスタする |

|

[VOD/KIT]一緒に動かそう!Lチカから始めるFPGA開発【基礎編&実践編】 開発ツールQuartusやFPGAボードDE10-Liteの動かし方から,本格的なディジタル回路設計を始めるために必要な知識を全般的に取得する |

|

[VOD/KIT]ARM Cortex-A9&FPGA内蔵SoC Zynqで初体験!オリジナル・プロセッサ開発入門 CPUとロジックの混載回路をワンチップ化し,リアルタイムOSで動かす |

|

[VOD/KIT]実習キットで一緒に作る!オープンソースCPU RISC-V入門 マイコンの基礎からRISC-Vコアとシステムの論理設計/開発環境構築/FPGA実装まで |